The VHDL variable assignment operator has

GitHub - ismailelbadawy/vhdl-cheat-sheet: This is a cheat sheet for vhdl to help when in doubt about syntax or buidling blocks. VHDL Synthesizer, see Appendix A, “Quick Reference.”. For a list of exceptions and constraints on the VHDL Synthesizer's support of VHDL, see Appendix B, “Limitations.” This chapter shows you the structure of a VHDL design, and then describes the primary building blocks of VHDL used to describe typical circuits for synthesis. The character set in VHDL’87 is 128 characters, in VHDL’93 it is 256 characters (see page 8, 56). The character set is divided into seven groups – Uppercase letters, Digits, Special characters, The space characters, Lo-wercase letters, Other special characters and format effector. Separators Separators are used to separate lexical elements.

In VHDL -93, a variable assignment may have a label: label: variable_name := expression; VHDL -93 supports shared variables which may be accessed by more than one process.However, the language does not define what happens if two or more processes make conflicting accesses to a shared variable at the same time.

VHDL assignments include the signal assignment operator with the less than equals assignment operator, and the colon equals variable assignment operator. The signal assignment operator operates and gets synthesized into silicon gates. So we have Z is assigned to A added with B, or Z is assigned to D after five nanoseconds in a simulation. In a variable assignment, it's colon equals and those assignments are updated immediately in the process such as; count :=count +1, or a:=27.

A variable also holds a single value of a given type. The value of the variable may be changed during the simulation by using variable assignment operator. Variables are used in the processes and subprograms. Variables are assigned by the assignment operator ':='. Example: variable index: integer :=0; 3. Signals. Signals can be declared in architecture and used anywhere within the architecture. Signals are assigned by the assignment operator '='. Example:

VHDL syntax Cheat Sheet

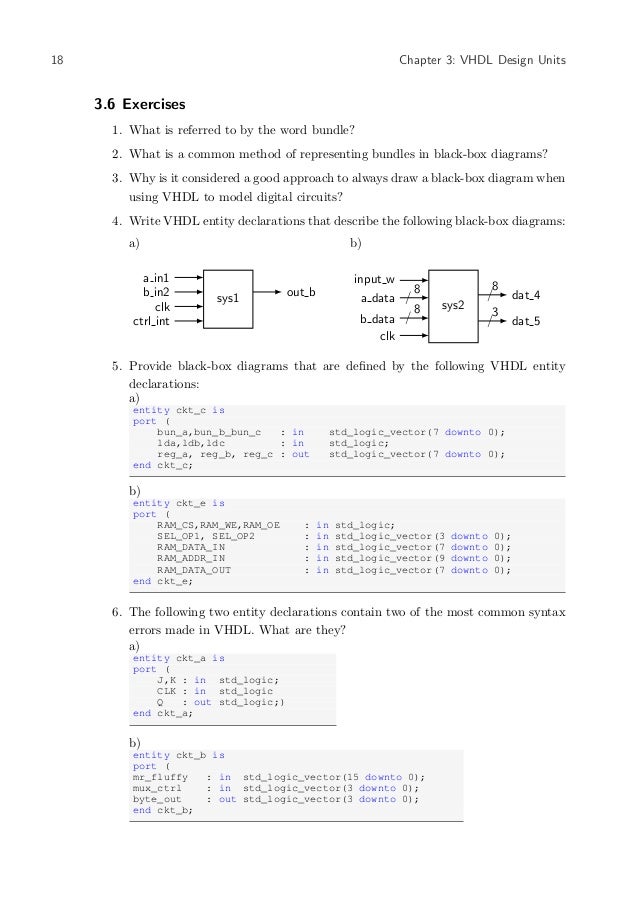

[PDF] VHDL Cheat-Sheet Concurrent Statements Sequential Statements, Description CKT Diagram VHDL Model. Typical logic circuit entity my_ckt is. Port ( A,B,C,D : in std_logic;. F : out std_logic); end my_ckt; architecture ckt1 of Description CKT Diagram VHDL Model Typical logic circuit entity my_ckt is Port ( A,B,C,D : in std_logic; F : out std_logic); end my_ckt; architecture ckt1 of my_ckt

[PDF] VHDL Quick Reference Card, VHDL Quick Reference Card. 1. Introduction. VHDL is a case insensitive and strongly typed language. Comments start with two adjacent hyphens (--) and end at. VHDL Quick Reference Card 1. fourvalIntroduction VHDL is a case insensitive and strongly typed language. Comments start with two adjacent hyphens (--) and end at end of line. 2. Compilation Units Library Usage Declarations -- ref. 11 Entity Declarations -- ref. 3 Architecture Declarations -- ref. 4 Package Declarations -- ref. 10

[PDF] VHDL Cheat Sheet, All VHDL modules or components consist of an entity and an architecture. The entity defines the inputs and outputs of the module (i.e., the ports), while the VHDL Module All VHDL modules or components consist of an entity and an architecture. The entity defines the inputs and outputs of the module (i.e., the ports), while the architecture defines the function of the module. Entity (Table 5-14, p. 259) Each port in the entity specifies a direction (IN or OUT) and a type (std_logic or std_logic_vector).

VHDL std_logic_vector assignment

Vhdl Reference Guide

[PDF] VHDL Syntax Reference, variable assignment, signal initialization. Example: signal q: std_logic_vector(3 downto 0);. Multiple bits are enclosed using a pair of double quotations:. If you want to assign an integer to an std_logic_vector, then you can do it like this. library IEEE; use IEEE.Std_Logic_1164.all; use IEEE.Numeric_STD.all; cl_ouput_ChA <= std_logic_vector(to_unsigned(12345, ch1_ouput_ChA'length)); -- natural cl_ouput_ChA <= std_logic_vector(to_signed(12345, ch1_ouput_ChA'length)); -- signed.

Simplifying VHDL Code: The Std_Logic_Vector Data Type , The VHDL keyword “std_logic_vector” defines a vector of elements of individual signal-assignment statements for ANDing the elements of The most common type used in VHDL is the std_logic. Think of this type as a single bit, the digital information carried by a single physical wire. The std_logic gives us a more fine-grained control over the resources in our design than the integer type, which we have been using in the previous tutorials. Normally, we want a wire in a digital interface to have either the value '1' or '0'.

How to write std_logic_vector assignment with input-dependent , SymbiYosys can use Verific as frontend to process VHDL, but Verific does not accept this. Here is a small piece of code which reproduces the I am aware that I can just write '11110000' and solve the problem. However, as a learning experience, I want to know what is wrong with this code and how to fix it. How do I assign value to std_logic_vector in 'chunks' in a single line? Thank you for your time.

VHDL language Reference manual

[PDF] IEEE Standard VHDL Language Reference Manual, (This introduction is not part of IEEE Std 1076, 2000 Edition, IEEE Standards VHDL Language Reference Manual.) The VHSIC Hardware (This introduction is not part of IEEE Std 1076, 2000 Edition, IEEE Standards VHDL Language Reference Manual.) The VHSIC Hardware Description Language (VHDL) is a formal notation intended for use in all phases of the creation of electronic systems. Because it is both machine readable and human readable, it supports the

IEEE 1076-2019, VHSIC Hardware Description Language (VHDL) is defined. VHDL IEEE 1076-2019 - IEEE Standard for VHDL Language Reference Manual. VHDL Reference Manual 2-1 2. Language Structure VHDL is a hardware description language (HDL) that contains the features of conventional programming languages such as Pascal or C, logic description languages such as ABEL-HDL, and netlist languages such as EDIF. VHDL also includes design management features, and

1076-2019, Scope: This standard defines the syntax and semantics of the VHSIC Hardware Description Language (VHDL). The acronym VHSIC (Very High IEEE Standard VHDL Language Reference Manual IEEE 3 Park Avenue New York, NY 10016-5997, USA 26 January 2009 IEEE Computer Society Sponsored by the Design Automation Standards Committee 1076 TM Authorized licensed use limited to: Milwaukee School of Engineering. Downloaded on January 26,2018 at 14:42:56 UTC from IEEE Xplore. Restrictions apply.

What are the two levels of VHDL module and how are they different

A design entity is a basic element in a VHDL model. It can have different levels of abstraction like gate, printed circuit board or the entire system. The different levels of abstraction is classified into: Behavorial; Dataflow; Structural; In VHDL, a design entity is a module (as in software system) with its inputs and output which are refered Osx high sierra update.

This example describes how to create a hierarchical design using VHDL. The top-level design, called top.vhd, implements an instance of the function logic.vhd. In the top.vhd file, a component for the logic function is declared inside the architecture in which it is instantiated. The Component Declaration defines the ports of the lower-level function.

VHDL is case insensitive module, you can use both upper case and lower case in this module. For example : Both ENTITY and entity will be considered as same. We have some rules to write entity name. The first letter of the entity should be alphabet. Special charcters should not be allowed except underscore(_). Two underscore(_) continously not allowed.

VHDL code examples

VHDL Tutorial: Learn by Example, The following example shows how to write the program to incorporate multiple components in the design of a more complex circuit. In order to simulate the Example 6 Barrel Shifter - architecture architecture behv of bs_vhdl is-- SHIFT LEFT/RIGHT FUNCTION function barrel_shift(din: in std_logic_vector(31 downto 0); dir: in std_logic; cnt: in std_logic_vector(4 downto 0)) return std_logic_vector is begin if (dir = '1') then return std_logic_vector((SHR(unsigned(din), unsigned(cnt)))); else

[PDF] VHDL Examples, Example 1. Odd Parity Generator - Testbench. --- This structural code instantiate the ODD_PARITY_TB module to create a. --- testbench for the odd_parity_TB Example of VHDL reading and writing disk files The VHDL source code is file_io.vhdl This example is a skeleton for a VHDL simulation that needs input from a file, simulates based on the input and produces output to a file. The output file may be used as input to other applications.

[PDF] VHDL examples, VHDL Tutorial. Behavioral VHDL. 4 to 1 Mux library ieee; use ieee.std_logic_1164.all; entity MUX41 is port. --define inputs and outputs. (. S1 : inbit;. -- input S1. VHDL Tutorial: Learn by Example-- by Weijun Zhang, July 2001 *** NEW (2010): See the new book VHDL for Digital Design, F. Vahid and R. Lysecky, J. Wiley and Sons, 2007. Concise (180 pages), numerous examples, lo

VHDL port STD_LOGIC_VECTOR

Simplifying VHDL Code: The Std_Logic_Vector Data Type , Similarly, the input ports b0, b1, and b2 can be grouped as another three-bit input port called b_vec. What the circuit does is AND an element of library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; use work.all; use work.bus_multiplexer_pkg.all; entity bus_multiplexer_4 is generic (bus_width : positive := 8); port ( bus0, bus1, bus2, bus3 : in std_logic_vector(bus_width - 1 downto 0); sel : in std_logic_vector(1 downto 0); o : out std_logic_vector(bus_width - 1 downto 0

Vectored Ports & Signals, The type of the port is STD_LOGIC_VECTOR, which is also defined in package an array type was used to allow the description in VHDL of a vectored port. Here’s how to use the IOBUF and to talk with the SRAM in your VHDL project. Add the following ports to your top-level VHDL component. SR_DAT : inout std_logic_vector(31 downto 0); --SRAM data bus SR_ADR : out std_logic_vector(? downto 0); --SRAM address bus SR_WEN : out std_logic; --SRAM write enable

VHDL Mini-Reference, vhdl. Is it possible to create an entity with a port that is an array of std_logic_vectors, with both the size of the array and the std_logic_vector coming from generics I am trying to connect one of my VHDL blocks to a Xilinx generated block (a dual port RAM). The problem is that the write enable of the RAM is defined as an std_logic_vector(0 down to 0) instead

Compilation and simulation of VHDL code

VHDL Compilation and Simulation with ModelSim, Examine and compile the code for this lab. 3.1 Using your favorite text editor, create a file called package.vhd with the following contents: PACKAGE resources IS. VHDL Compilation and Simulation with ModelSim 1. What you will learn . 1.1 How to create a working directory for the VHDL tools. 3.2 Compile the VHDL code:

[PDF] Tutorial on VHDL Compilation, Simulation, and Synthesis, Tutorial on VHDL Compilation, Simulation, and Synthesis. USING MENTOR by adding the following line in your VHDL program. code in this window. As you Make sure that the source file name has the extension of vhdl (if not, then use: mv orig_filename my4bit_full_adder.vhdl). Compile the source file by, alcom my4bit_full_adder.vhdl -work adder_models -nosynchk Once the compilation is successful, you will invoke the autologic program (in a batch mode) by typing following multi -line command:

Writing, Compiling, Debugging, and Simulating VHDL, Your compiled vhdl code units will be placed here. Note that we invoke the simulator on the entity name we are interested in, not the file which contains the Introduce the fundamental parts of the VHDL language Allow you to familiarize with the tool by let you debug a piece of VHDL code compile and simulate a small VHDL design Note:Don't get hung up on understanding all that is going on in the code. (**This note is a copy of the Roger Traylor's original note.) 2.0 Create directory and library structures

More Articles

This is my on-line scrapbook and/or blog.

I use it to collect information and make notes on everything I find useful and interesting.

The main focus will be Embedded Systems Architecture.

This means mainly embedded electronics, embedded software, mechanics and open source hardware and software.

Cheat Sheet Isaac

Due to the limited amount of time I have, to moderate comments I have disabled this option, however I do want to hear from you if you have remarks, suggestions, language improvements and/or questions. Please use the contact form.

Vhdl Cheat Sheet Pdf

Mysql mac start server. Thanks, Robert.